Wesentliche Erkenntnisse

- Die hardwareseitige Auslegung von Leistungsschaltern und die Schutzkoordination lassen sich mit dem softwareseitigen Circuit-Breaker-Entwurfsmuster kombinieren, um Systeme ganzheitlich resilient zu gestalten.

- Eine fundierte Leistungsschalterauslegung beginnt auf Systemebene: Selektivität, Fehlerströme und Umgebungsbedingungen stehen vor der Detailkonstruktion.

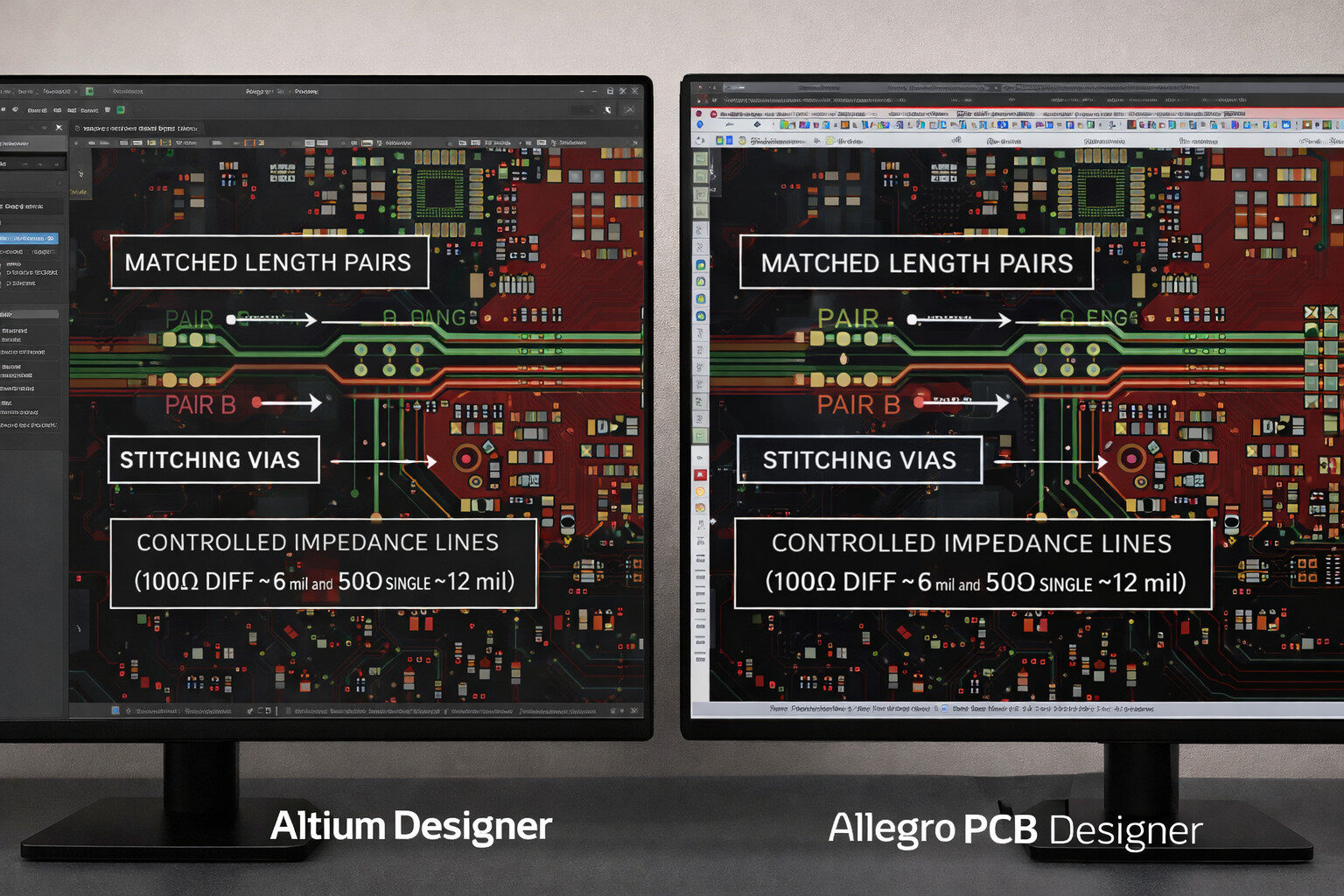

- Ein abgestimmter ECAD-Workflow (z. B. Altium Designer und Cadence Allegro) unterstützt konsistente Layout- und Fertigungsdokumentation.

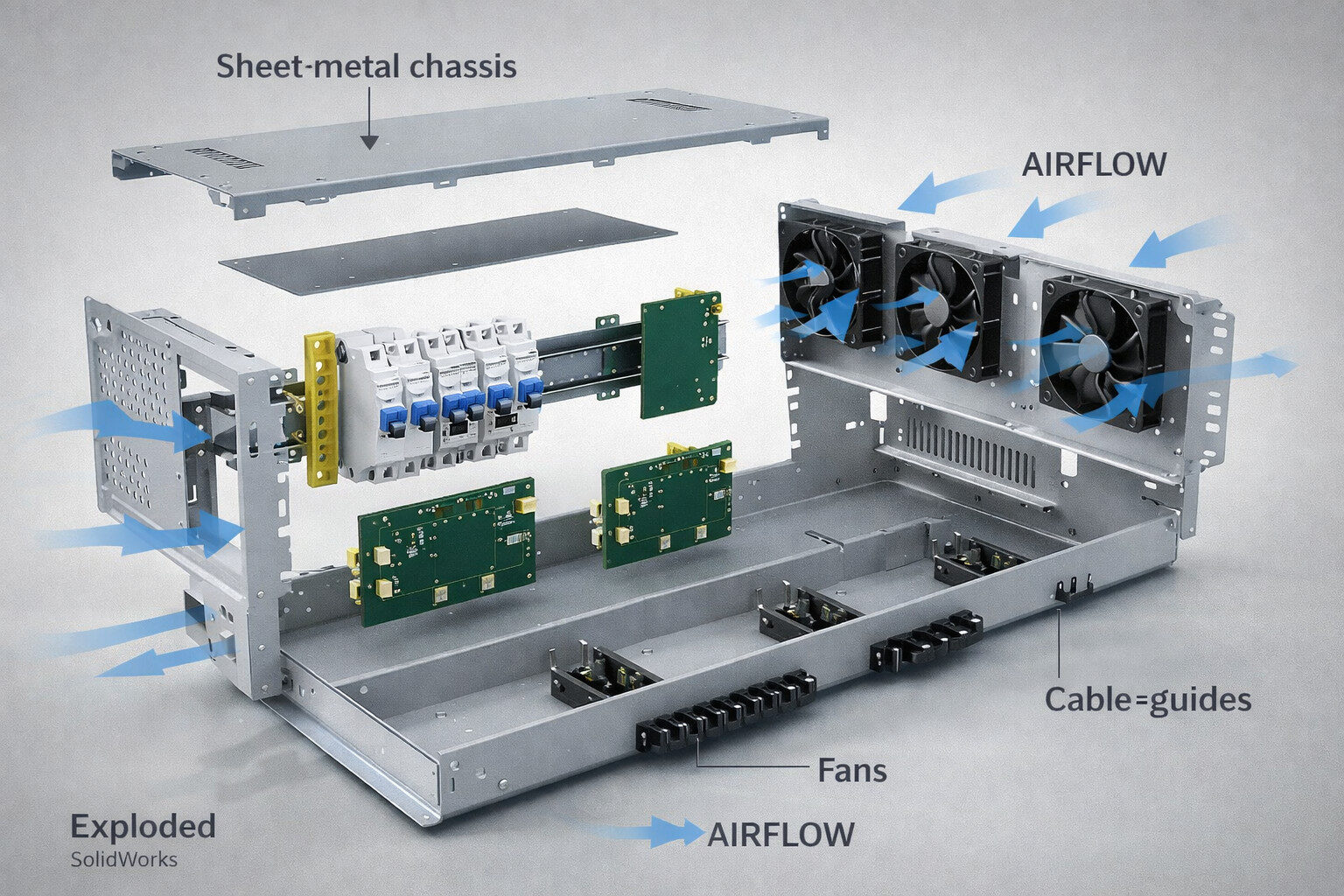

- Die Integration von MCAD (z. B. SolidWorks) reduziert mechanische Konflikte und verbessert die Abstimmung mit der Elektronikentwicklung.

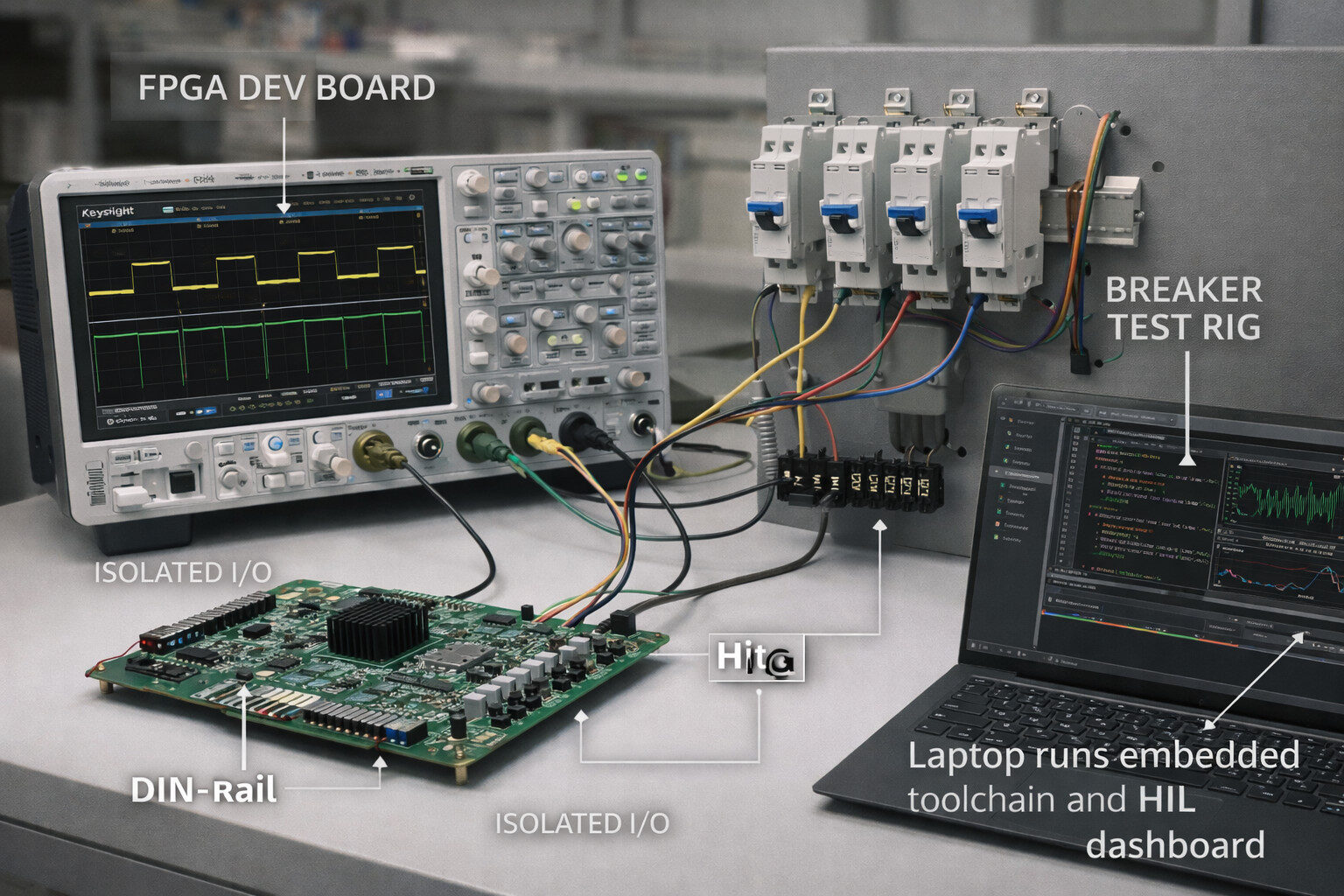

- FPGA- und Embedded-Design ermöglichen deterministische I/Os sowie Hardware-in-the-Loop(HIL)-Validierung.

- Bei Modernisierungen ist ein strukturiertes Retrofit-Design erforderlich, um bestehende Anlagen an aktuelle Anforderungen anzupassen.

Moderne Entwicklungsteams arbeiten häufig mit zwei unterschiedlichen „Leistungsschaltern“:

- Dem physischen Schutzgerät in Energieverteilungsanlagen.

- Dem Software-Resilienzmuster in verteilten IT-Systemen.

Beide verfolgen dasselbe Ziel: Störungen begrenzen und Folgewirkungen vermeiden. Dieser Beitrag zeigt, wie sich elektrische Schutztechnik, Software-Architektur sowie ECAD/MCAD- und FPGA-Workflows in einem integrierten Entwicklungsprozess zusammenführen lassen.

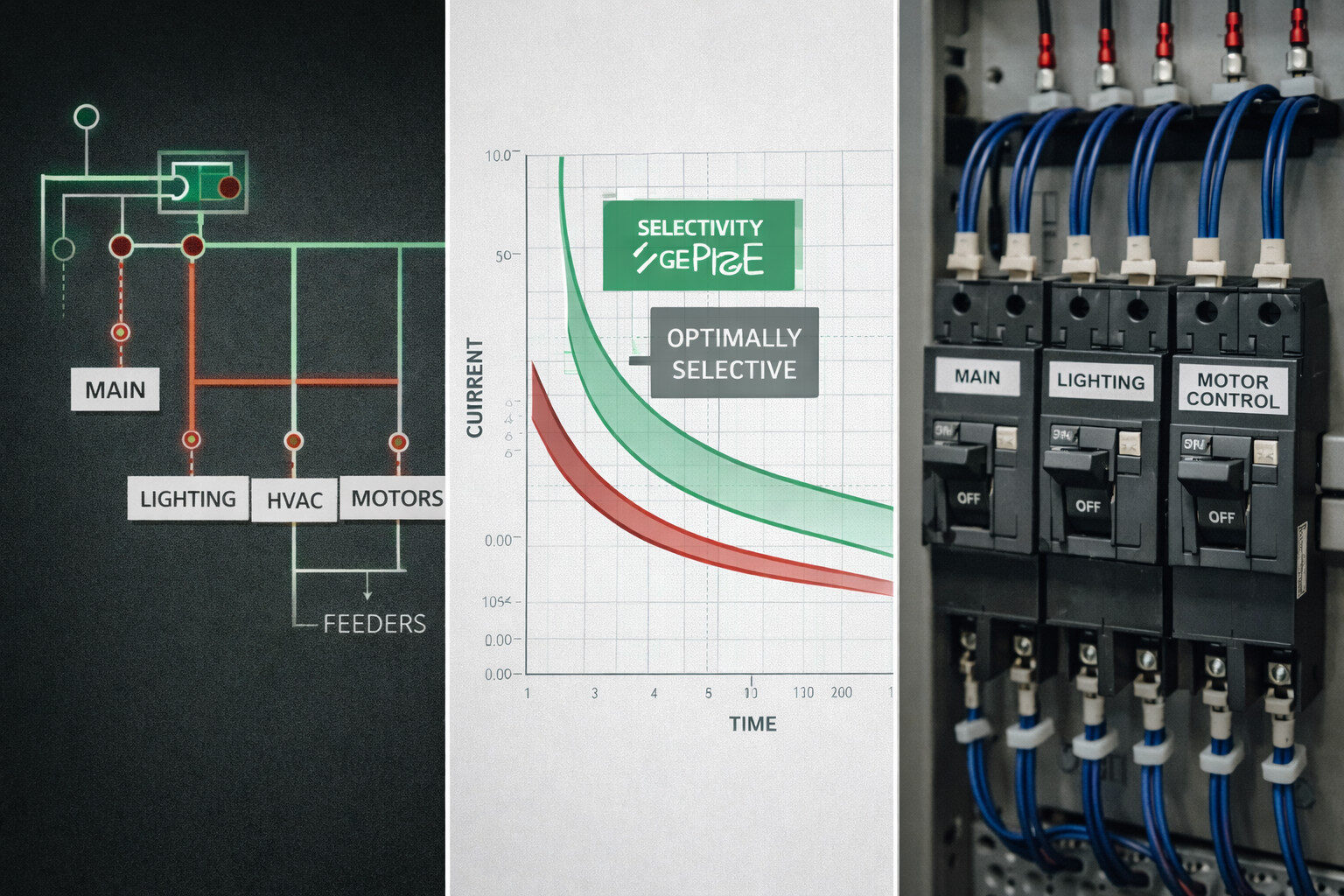

Teil 1 – Hardware: Leistungsschalterauslegung und Feldkoordination

In der Energieverteilung ist ein Leistungsschalter dafür ausgelegt, anormale Ströme innerhalb einer definierten Zeit-Strom-Kennlinie zu unterbrechen.

Eine strukturierte Leistungsschalterauslegung umfasst in der Regel:

- Kurzschluss- und Fehlerstromanalysen

- Selektivitäts- und Koordinationsstudien

- Bewertung der Umgebungsbedingungen

Vor der finalen Auslegung einer Schalttafel werden typischerweise folgende Aspekte geprüft:

Selektivität und Koordination

- Nachgelagerte Schutzgeräte sollen vor vorgelagerten auslösen.

- Zeit-Strom-Kennlinien müssen abgestimmt sein, um ungewollte Abschaltungen zu vermeiden.

Thermische Randbedingungen und Derating

- Umgebungstemperatur und Gehäusebedingungen beeinflussen das Auslöseverhalten.

- Leitererwärmung und Wärmeabfuhr sind zu berücksichtigen.

Dokumentation

- Einliniendiagramme

- Schutz- und Koordinationsnachweise

- Prüfprotokolle

Diese Unterlagen sind für technische Abnahmen und Audits relevant.

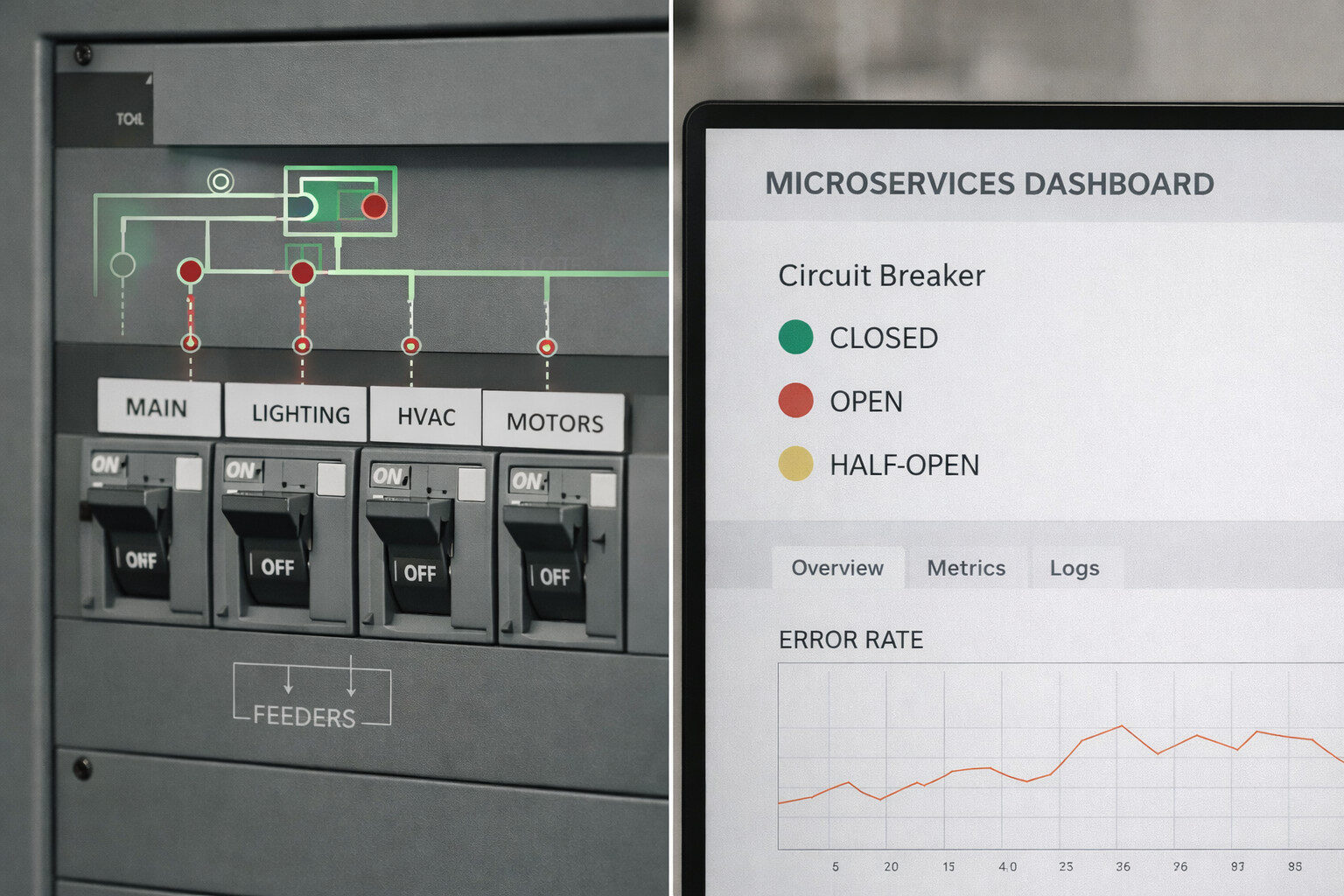

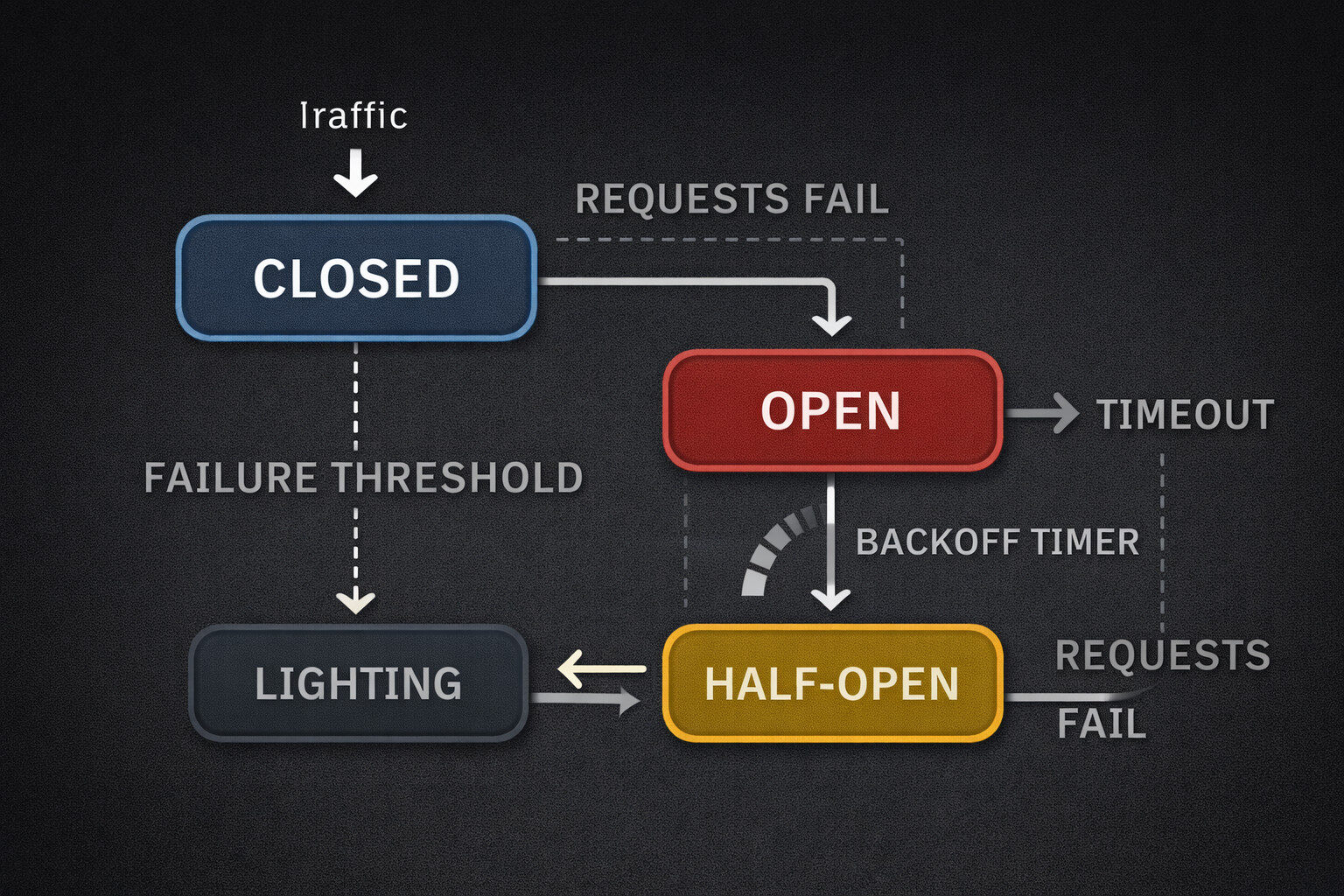

Teil 2 – Software: Das Circuit-Breaker-Entwurfsmuster

Das Circuit-Breaker-Entwurfsmuster schützt Anwendungen vor instabilen oder überlasteten Abhängigkeiten.

Werden definierte Schwellwerte – etwa Fehlerraten oder Latenzen – überschritten, wechselt der Breaker in den Zustand „Offen“. Anfragen werden blockiert oder über Fallback-Mechanismen verarbeitet. Nach einer Wartezeit erfolgt ein Übergang in den Zustand „Halb-offen“, um die Wiederherstellung zu prüfen. Erst danach wird der Zustand „Geschlossen“ wiederhergestellt.

Typische Messgrößen

- Gleitende Fehlerrate

- P99-Latenz

- Timeouts

- Backoff- und Retry-Metriken

Zustandsmodell

- Geschlossen → Offen → Halb-offen

- Häufig kombiniert mit exponentiellem Backoff

Beobachtbarkeit

- Statusereignisse des Breakers

- Fallback-Zähler

- Alarme im Kontext definierter Service-Level-Objectives (SLOs)

Einheitliche Konfigurations- und Monitoring-Standards erleichtern die teamübergreifende Einführung.

Teil 3 – ECAD: Strukturierter PCB-Layout-Workflow

Eine zuverlässige Hardwareentwicklung erfordert konsistente PCB-Designprozesse.

Ein typischer ECAD-Workflow kann beinhalten:

- Schematic Capture und Layout in Altium Designer

- Regel- und Constraint-Validierung in Cadence Allegro

- Fertigbarkeitsprüfungen (DFM)

- Design-Rule-Checks (DRC) pro Release

Wesentliche Ziele sind:

- Konsistente Impedanzkontrolle

- Saubere Rückstrompfade

- Eindeutige Net-Klassendefinitionen

- Fertigungsreife Dokumentation

Eine toolübergreifende Validierung kann helfen, Layoutabweichungen frühzeitig zu erkennen.

Teil 4 – MCAD: Mechanik, Packaging und Integration

Die mechanische Integration beeinflusst Zuverlässigkeit und Wartbarkeit maßgeblich.

Mit SolidWorks lassen sich unter anderem modellieren:

- Bauraum und Freiräume

- Kabelbaum-Biegeradien

- Kühl- und Luftführungswege

- Servicezugänge

Ein strukturierter ECAD–MCAD-Abgleich reduziert Kollisionsrisiken und vermeidet späte Designänderungen.

Teil 5 – FPGA und Embedded-Integration

Für Anwendungen mit deterministischen Anforderungen oder kurzen Regelzyklen kommen FPGA-basierte Architekturen zum Einsatz.

Typische Einsatzfelder sind:

- Signalverarbeitung

- Sicherheitsverriegelungen

- Zeitkritische I/O-Verarbeitung

HIL-Testumgebungen unterstützen die Validierung von Timing und Interaktionen zwischen Hardware und Firmware. Änderungen in Elektronik und Mechanik können über einen gemeinsamen digitalen Entwicklungsprozess nachvollzogen werden.

Quick-Start-Checkliste

Hardware

- Fehlerstrom- und Selektivitätsstudien vor der Verdrahtung abschließen.

- Thermische Randbedingungen dokumentieren.

Software

- Circuit-Breaker-Muster mit klar definierten Schwellwerten implementieren.

- Monitoring und Alarmierung einheitlich gestalten.

ECAD/MCAD

- DRC- und Kollisionsprüfungen pro Release durchführen.

- Constraint-Definitionen konsistent halten.

Validierung

- Fehlerfälle simulieren.

- HIL-Tests dokumentieren.

- Ergebnisse nachvollziehbar archivieren.

Integrierter Entwicklungsansatz

Die Verbindung von elektrischer Schutztechnik, Software-Resilienz und abgestimmten ECAD/MCAD/FPGA-Prozessen unterstützt eine strukturierte Produktentwicklung.

Ein solcher Ansatz kann dazu beitragen, technische Risiken frühzeitig zu identifizieren und die Abstimmung zwischen den Disziplinen zu verbessern.